Similar Posts

PCIe | SV | UVM | Verification

PCIe | SV | UVM | VerificationTypedef and Associative array in System Verilog

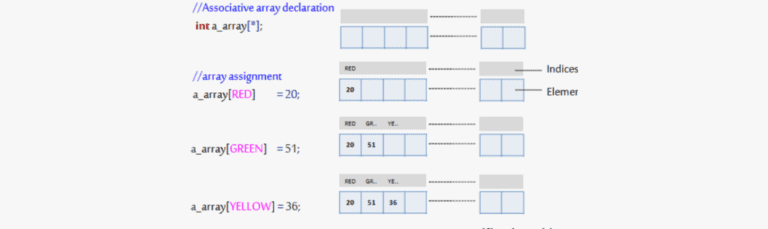

An associative array is one of the aggregate data types available in the system Verilog. … When the size of the collection is unknown or the data space is sparse, an associative array is used, which does not have any storage allocated until it is used. That means, it is dynamically allocated but has non-contiguous elements.

Understanding Clocking Blocks in SystemVerilogPart 1 of 2

Welcome to the first installment of our two-part series on preventing race conditions with clocking blocks in SystemVerilog. In the realm of digital design and verification, precise timing is paramount. Ensuring that signals change at the right moments, relative to clock edges, is crucial to the proper operation of digital systems. SystemVerilog, a versatile hardware…

PCIe | SV | UVM | Verification

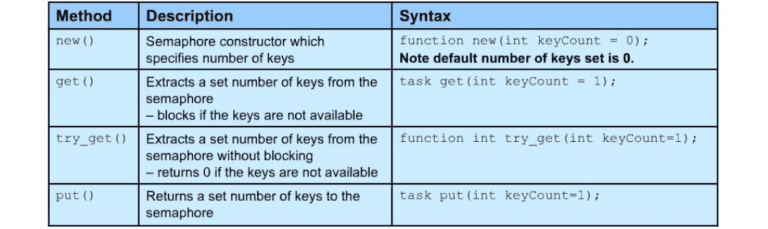

PCIe | SV | UVM | VerificationQueue and Semaphore in System Verilog

A mailbox is a built-in class around a queue that uses semaphores to control access to the ends of a queue. A mailbox only has FIFO element ordering whereas you can access the head, tail, or middle elements of a queue. … However, if there is more than one thread, a mailbox is a convenient class to use.

PCIe | SV | UVM | Verification

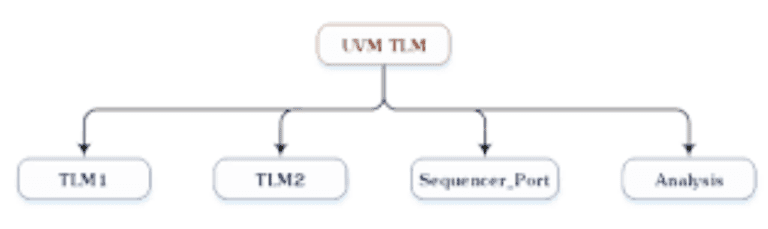

PCIe | SV | UVM | VerificationTLM in UVM- Introduction

Transaction Level Modeling is a modeling style for building highly abstract models of components and systems. In this scheme, data is represented as transactions (class objects that contain random, protocol-specific information) that flow in and out of different components via special ports called TLM interfaces.

PCIe | SV | UVM | Verification

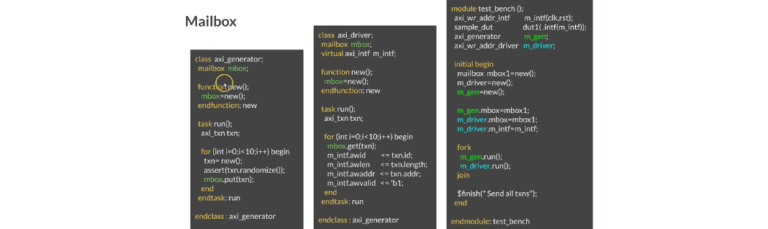

PCIe | SV | UVM | VerificationMailbox

Mailboxes are a message-based process synchronization and communication mechanism provided in SV. It allows messages to be exchanged between processes. Conceptually, mailboxes behave like real mailboxes with delivery and retrieval of messages

PCIe | SV | UVM | Verification

PCIe | SV | UVM | VerificationQueue in System Verilog

A SystemVerilog queue is a First In First Out scheme which can have a variable size to store elements of the same data type. It is similar to a one-dimensional unpacked array that grows and shrinks automatically. They can also be manipulated by indexing, concatenation, and slicing operators.

One Comment

Comments are closed.

nice!